Not your typical lobste. rs link-dumper or book-cover–posting zombie.

For instance, Sky130A 130nm process node have upto 5 metal layers.

bsky.app/profile/roha...

Imagine it, then put it into silicon.

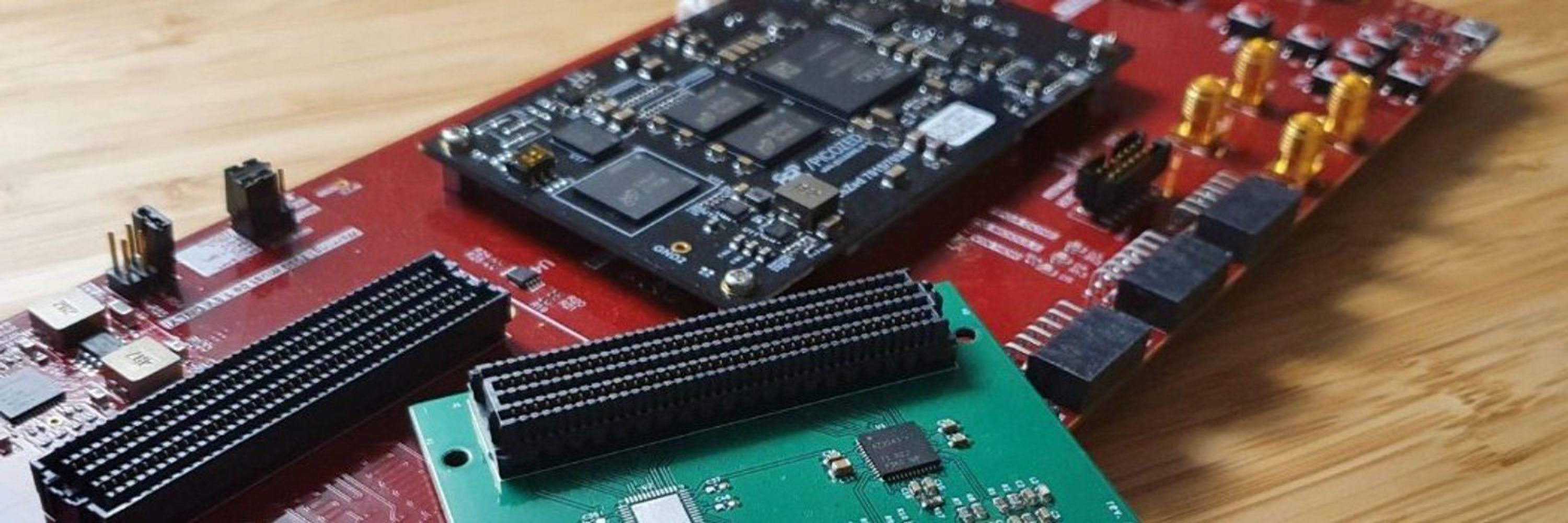

Made by Vicharak aka @aksharvastarpara.bsky.social 's team and two FPGA freaks.

Check - t.co/vBGGA2i0uX

Thanks @mattvenn.net and @urishaked.bsky.social and whole @tinytapeout.com team for making this possible.

For instance, Sky130A 130nm process node have upto 5 metal layers.

bsky.app/profile/roha...

Metal 1: used for local interconnects, this allowed short and dense wiring.

Metal 2: used for global signals like buses, clocks, power.

Metal 1: used for local interconnects, this allowed short and dense wiring.

Metal 2: used for global signals like buses, clocks, power.

Another mike bell project to fab!

Another mike bell project to fab!

Nice idea for analog tapeout for some day.

Nice idea for analog tapeout for some day.

Although the element size is capped at 32 bits, the wide vector registers (256 bits) still allow multiple elements to be processed simultaneously.

Although the element size is capped at 32 bits, the wide vector registers (256 bits) still allow multiple elements to be processed simultaneously.

with 60% brightness. It needs a external supply for 100% brightness.

with 60% brightness. It needs a external supply for 100% brightness.

*This is the one for storing TV codes for that IR LED project

*and not the atari one

*This is the one for storing TV codes for that IR LED project

*and not the atari one

www.tinytapeout.com/chips/tt07/t...

www.tinytapeout.com/chips/tt07/t...

It's a static power estimation obviously. Also it's a digital tapeout, so I don't expect it to be a very power hungry design (assuming SKY130A cells are optimized).

It's a static power estimation obviously. Also it's a digital tapeout, so I don't expect it to be a very power hungry design (assuming SKY130A cells are optimized).

bsky.app/profile/roha...

TT FPGA controls seven-segment display via spi-slave and the RP2040 just sends it a 6-bit message to light up the LEDs.

bsky.app/profile/roha...

Come for India and you'll get a bloody nose.

Come for India and you'll get a bloody nose.