Not your typical lobste. rs link-dumper or book-cover–posting zombie.

It was one of the first NMOS processes to use separate metal layers for local connections and global signals.

It was one of the first NMOS processes to use separate metal layers for local connections and global signals.

Nice idea for analog tapeout for some day.

Nice idea for analog tapeout for some day.

Each one has 128 analog switches.

We can do 8x16 analog array with one.

So this is actually a analog matrix.

Each one has 128 analog switches.

We can do 8x16 analog array with one.

So this is actually a analog matrix.

It has been prototyped on a Xilinx Ultrascale Plus FPGA platform.

github.com/google-coral...

It has been prototyped on a Xilinx Ultrascale Plus FPGA platform.

github.com/google-coral...

He may be a tad racist, but a great guy. I mean all Indians are racist to each other, who cares.

www.computerhistory.org/revolution/m...

He may be a tad racist, but a great guy. I mean all Indians are racist to each other, who cares.

www.computerhistory.org/revolution/m...

Imagine it, then put it into silicon.

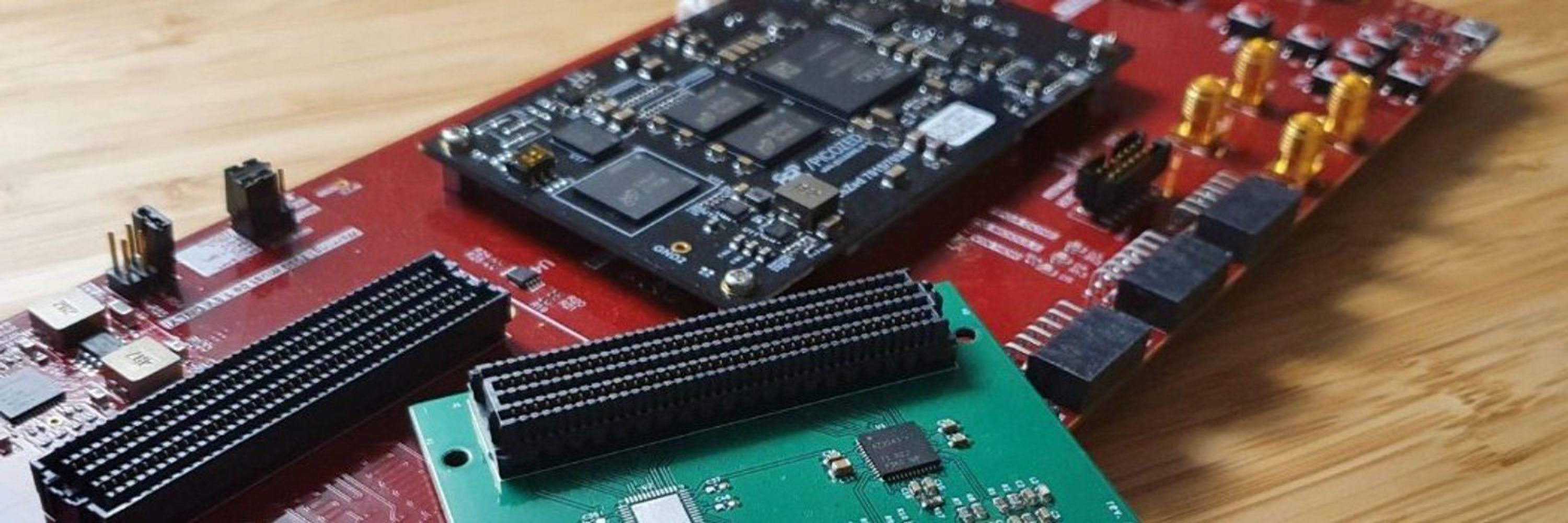

Made by Vicharak aka @aksharvastarpara.bsky.social 's team and two FPGA freaks.

Check - t.co/vBGGA2i0uX

Thanks @mattvenn.net and @urishaked.bsky.social and whole @tinytapeout.com team for making this possible.

Imagine it, then put it into silicon.

Made by Vicharak aka @aksharvastarpara.bsky.social 's team and two FPGA freaks.

Check - t.co/vBGGA2i0uX

Thanks @mattvenn.net and @urishaked.bsky.social and whole @tinytapeout.com team for making this possible.

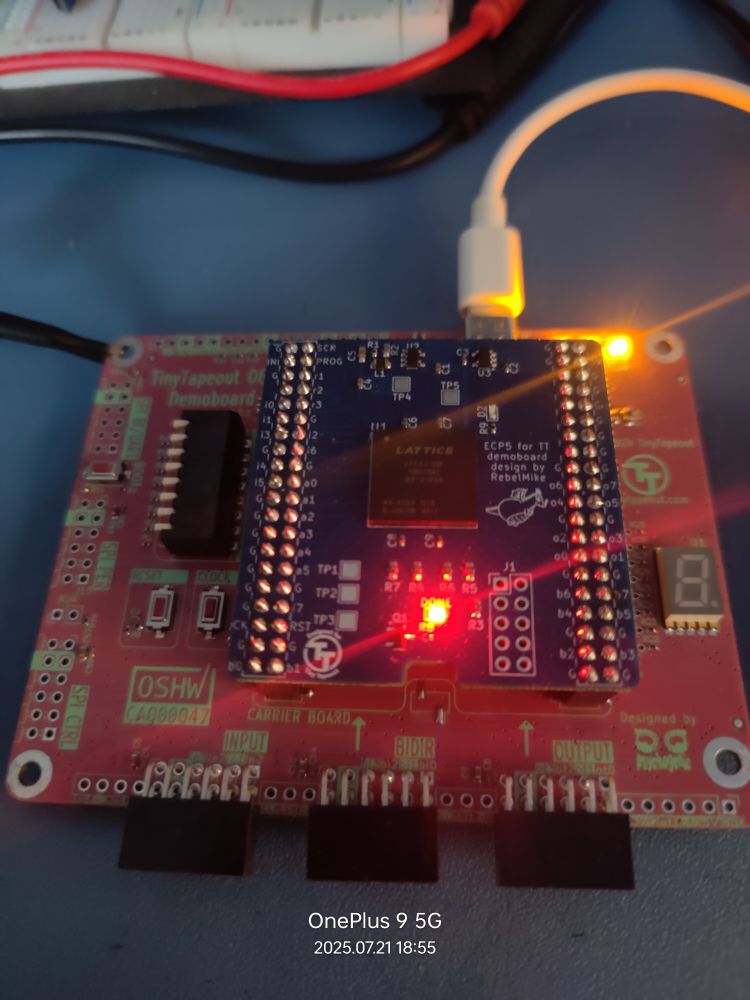

TT FPGA controls seven-segment display via spi-slave and the RP2040 just sends it a 6-bit message to light up the LEDs.

TT FPGA controls seven-segment display via spi-slave and the RP2040 just sends it a 6-bit message to light up the LEDs.

Come for India and you'll get a bloody nose.

Come for India and you'll get a bloody nose.

FPGAs are ❤️.

FPGA brother to tinytapeout ASIC by Michael Bell aka @rebelmike.bsky.social

@tinytapeout.com @mattvenn.net @urishaked.bsky.social

FPGAs are ❤️.

FPGA brother to tinytapeout ASIC by Michael Bell aka @rebelmike.bsky.social

@tinytapeout.com @mattvenn.net @urishaked.bsky.social

And after uploading blinky, I should observe 2.5v on TP5, right ?

bsky.app/profile/roha...

And after uploading blinky, I should observe 2.5v on TP5, right ?

bsky.app/profile/roha...

Now trying to get it to work as intended.

Now trying to get it to work as intended.

It is not able to read ECP5 ID, now what? ( there is power LED on fpga though)

It is not able to read ECP5 ID, now what? ( there is power LED on fpga though)

Had to visit a nearby university to get the X-ray inspection done.

Had to visit a nearby university to get the X-ray inspection done.

I don't have a design on this but I intend to try RISC-V SoCs on this.

@tinytapeout.com @mattvenn.net

I don't have a design on this but I intend to try RISC-V SoCs on this.

@tinytapeout.com @mattvenn.net