No sources or exclusive info

oh, and fuck corp publishing.

www.theverge.com/news/695969/...

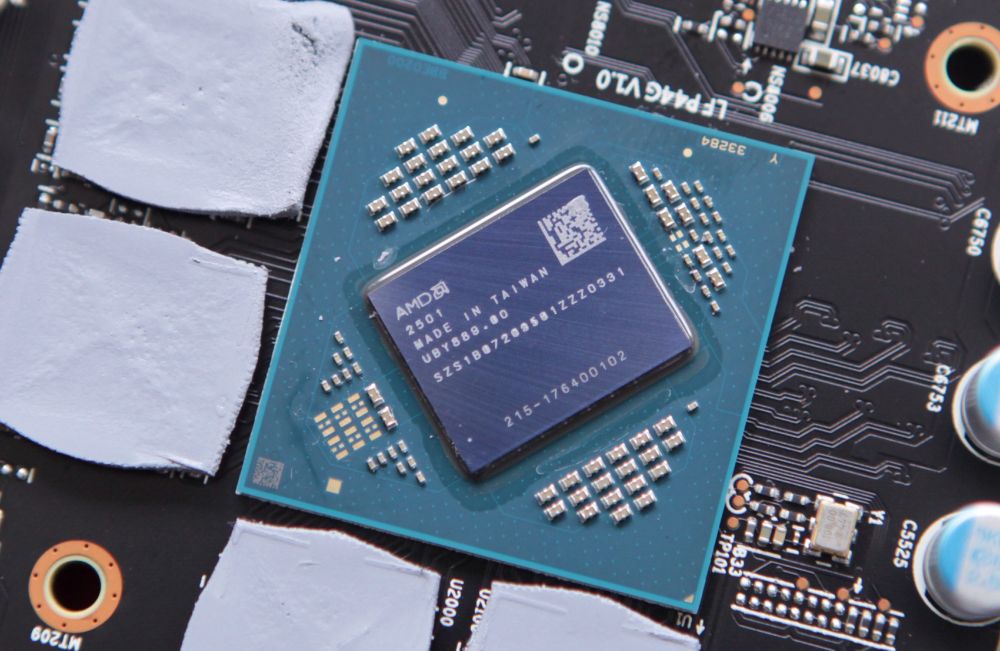

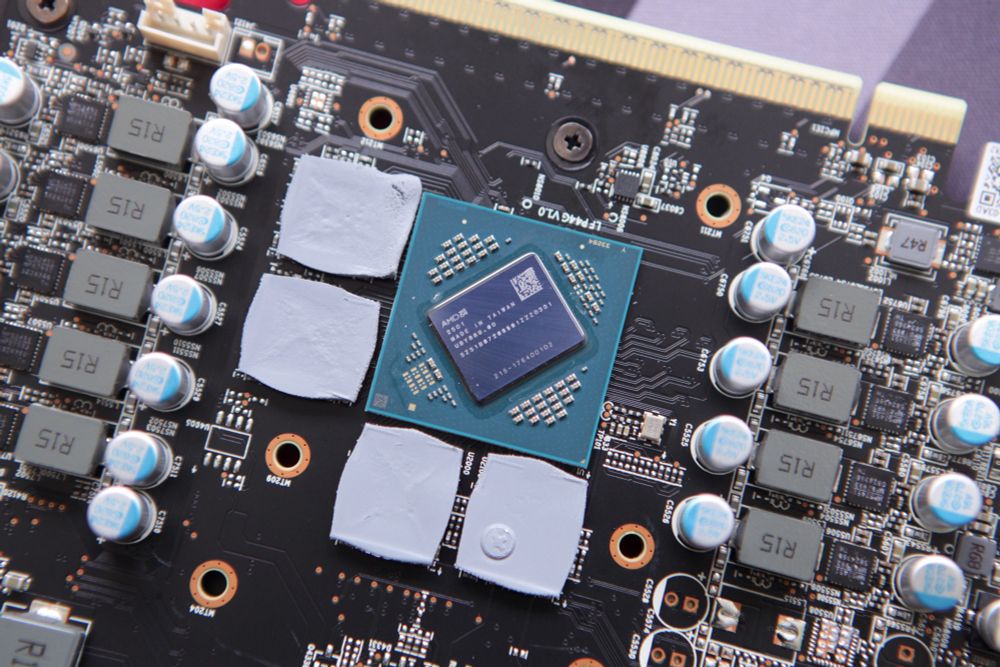

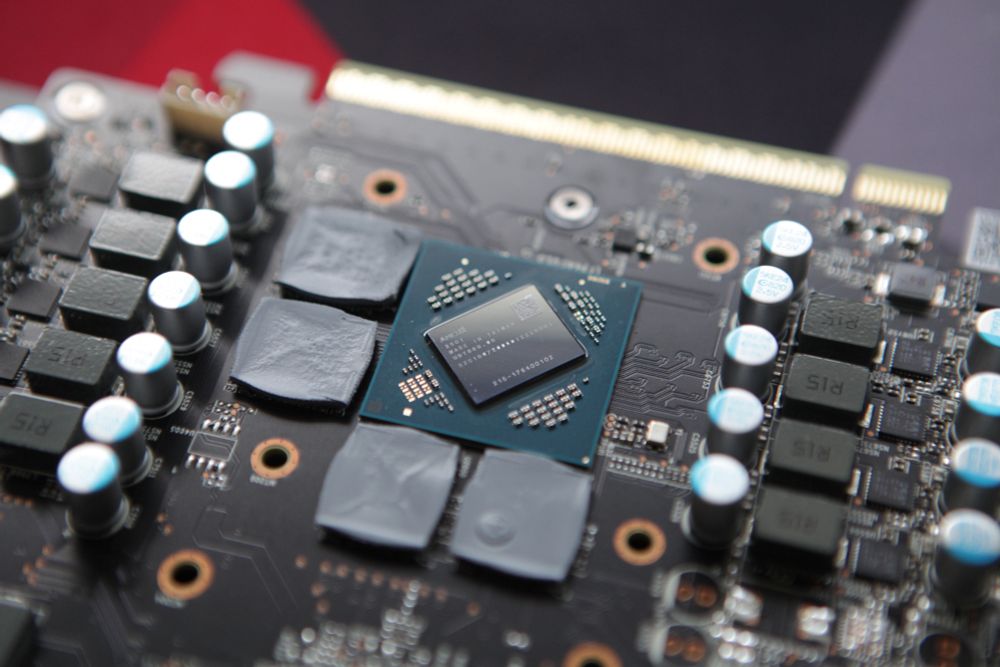

- 29.7 Billion Transistors

- 199 mm² Die Size

- 29.7 Billion Transistors

- 199 mm² Die Size

www.intel.com/content/www/...

www.intel.com/content/www/...

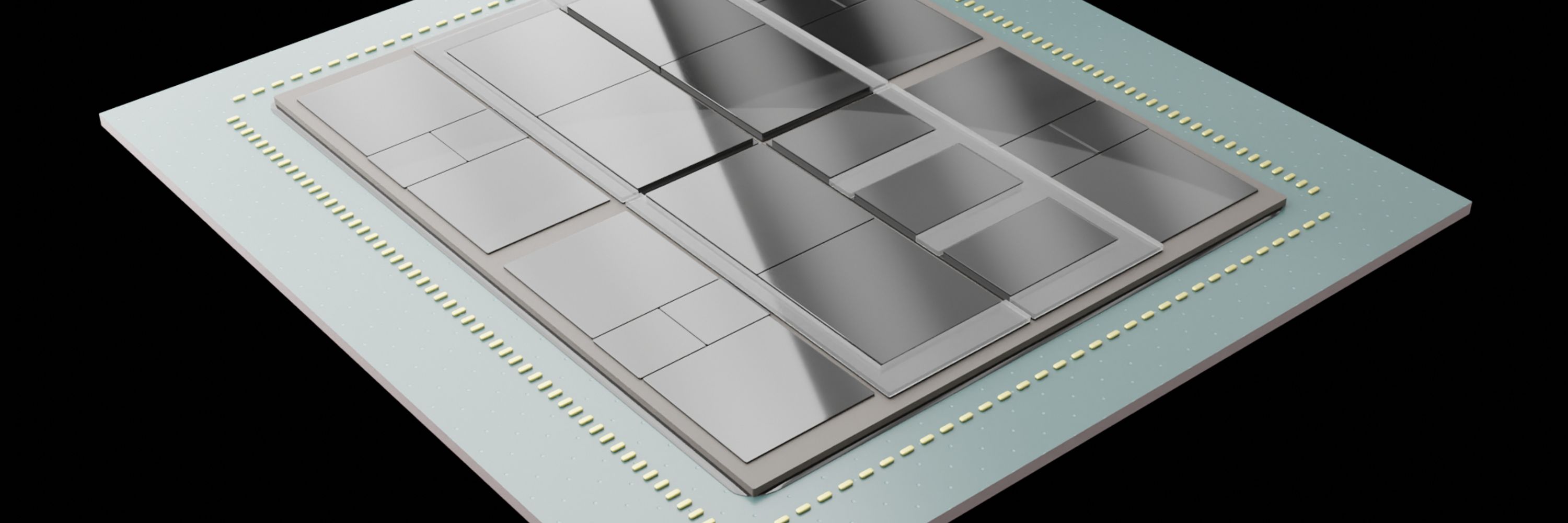

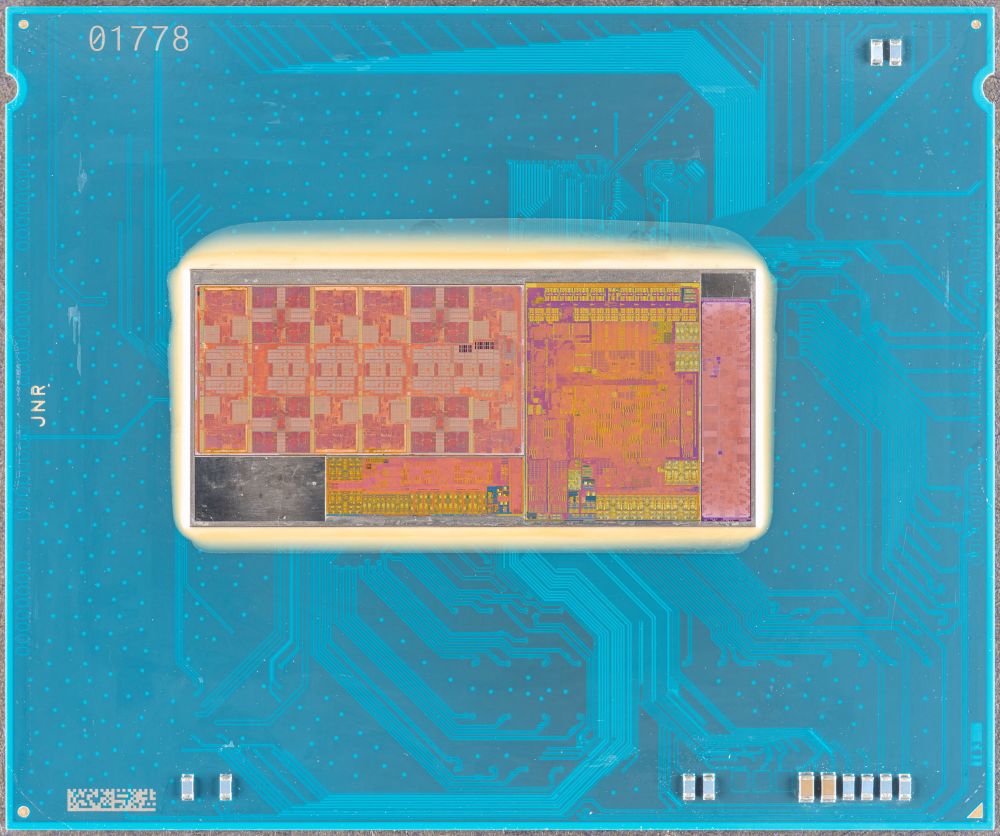

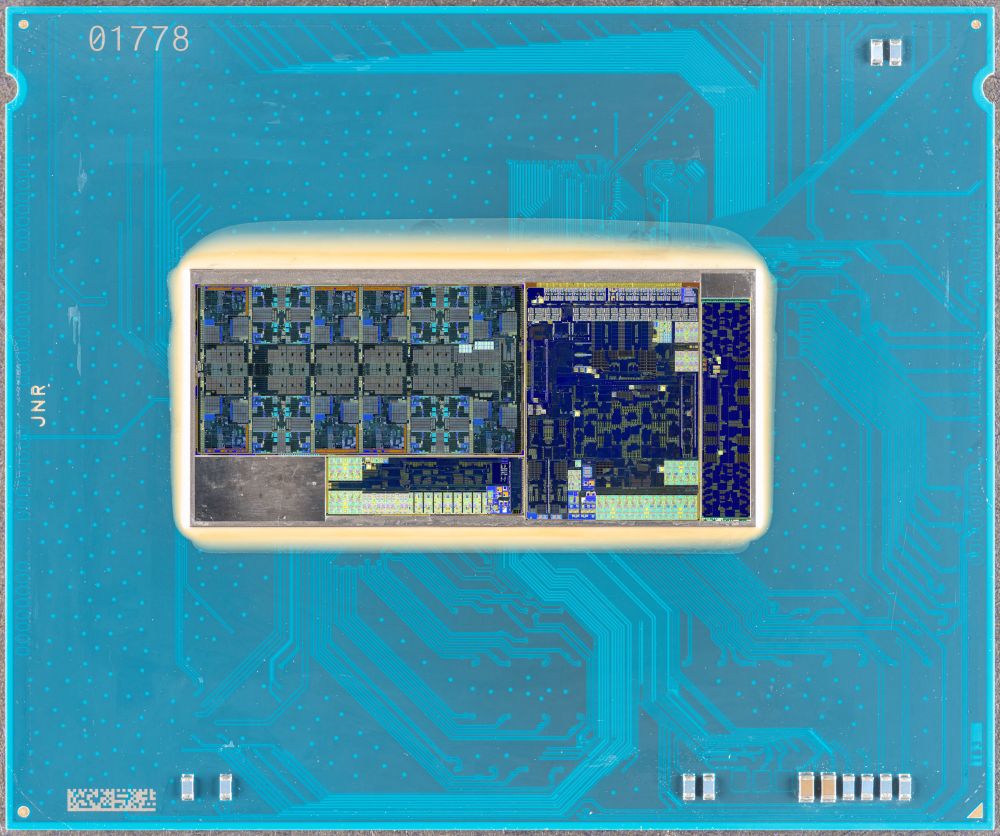

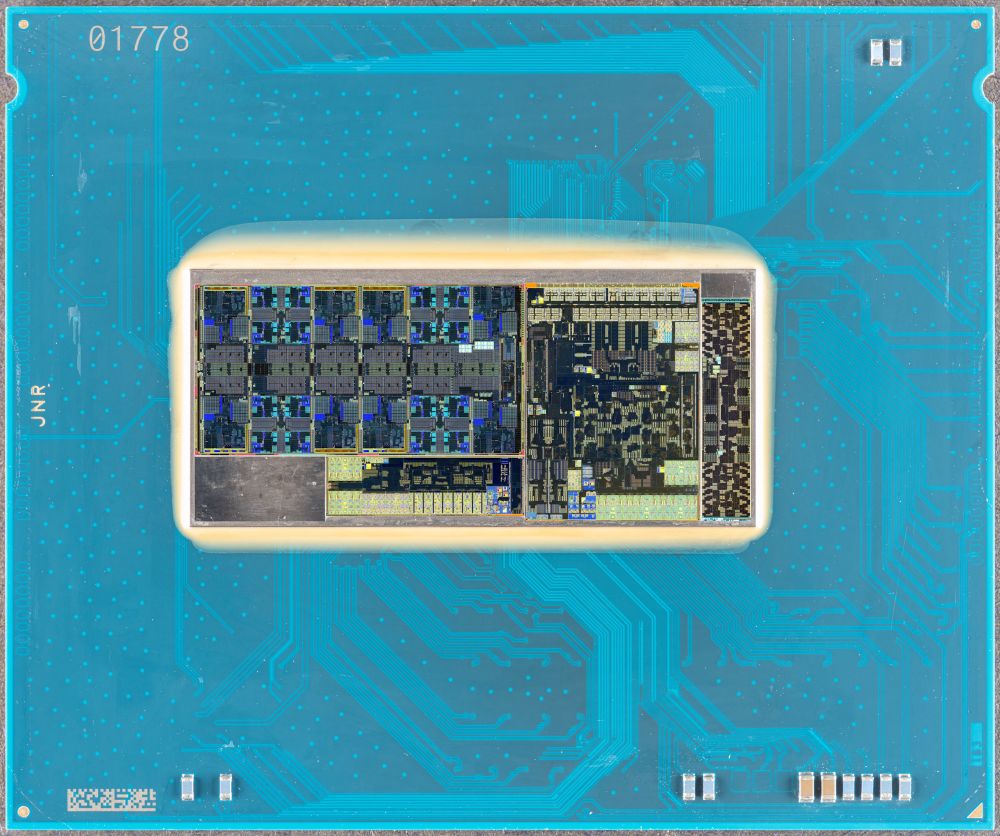

Arrow Lake-S die shots projected on the full package.

Full resolution: www.flickr.com/photos/13056...

Arrow Lake-S die shots projected on the full package.

Full resolution: www.flickr.com/photos/13056...

Venice Dense SP7 → 8 CCD * 32 = 256 cores

?

🤔

Could more closely mirror Intel's 2 platform strategy, especially if SP8 supports 2P configurations

Venice Dense SP7 → 8 CCD * 32 = 256 cores

?

🤔

Could more closely mirror Intel's 2 platform strategy, especially if SP8 supports 2P configurations

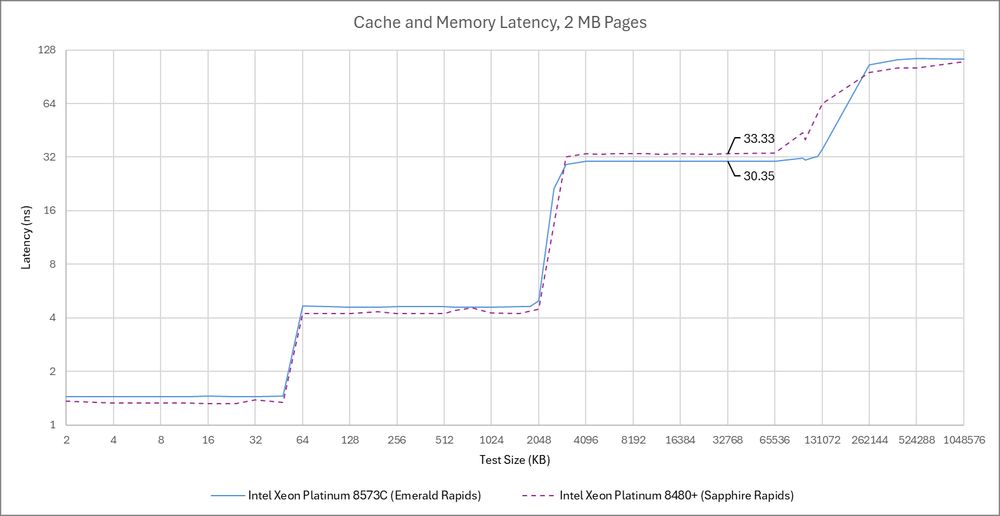

www.computerenhance.com/p/an-intervi...

www.computerenhance.com/p/an-intervi...

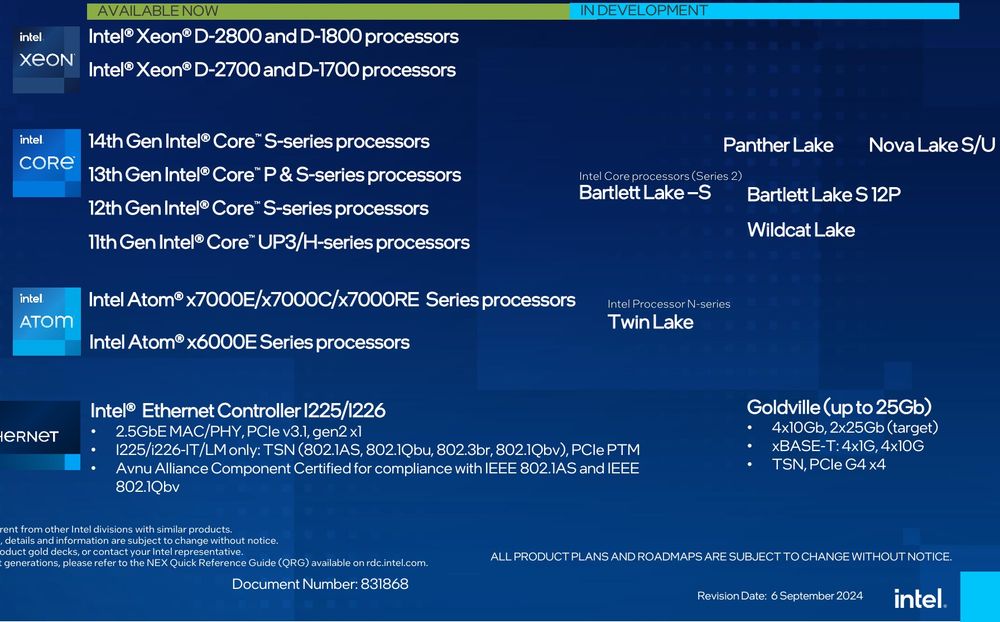

www.intel.com/content/www/...

www.intel.com/content/www/...

In before 8P16E dies get canned in favour of double 4P8E or 6P8E compute tiles for Nova Lake-S

I just can't take 2x8P16E at face value after the cancellation of 8P32E Arrow Lake

It's not like a 12P16E4e flagship with Big LLC would be *that* uncompetitive with Medusa, right?

In before 8P16E dies get canned in favour of double 4P8E or 6P8E compute tiles for Nova Lake-S

I just can't take 2x8P16E at face value after the cancellation of 8P32E Arrow Lake

It's not like a 12P16E4e flagship with Big LLC would be *that* uncompetitive with Medusa, right?

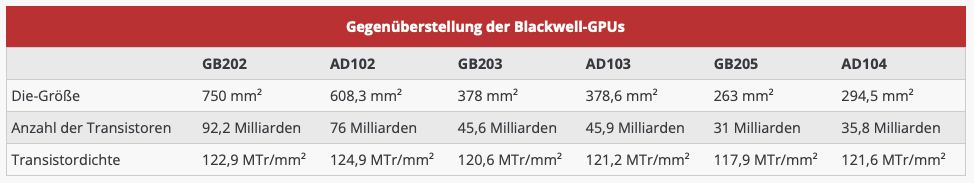

Source: www.hardwareluxx.de/index.php/ar...

Source: www.hardwareluxx.de/index.php/ar...

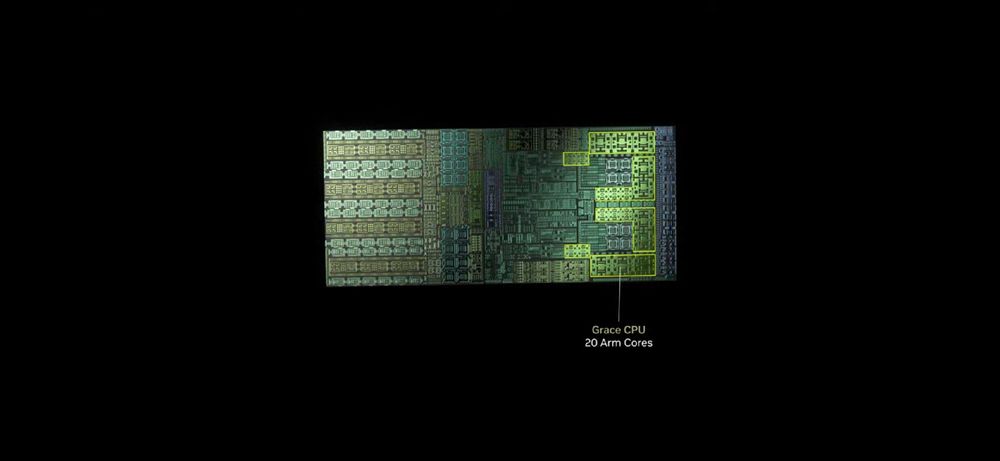

Because otherwise why would it have an asymmetric CPU layout?

Looks like 2 clusters with 5x Cortex-X + 5x Cortex-A each

It also seems to have all the I/O you'd want for a Laptop

"1000 FP4 TOPS" (24TPCs?) would correspond GB205 (5070Ti Laptop) performance

Because otherwise why would it have an asymmetric CPU layout?

Looks like 2 clusters with 5x Cortex-X + 5x Cortex-A each

It also seems to have all the I/O you'd want for a Laptop

"1000 FP4 TOPS" (24TPCs?) would correspond GB205 (5070Ti Laptop) performance