No sources or exclusive info

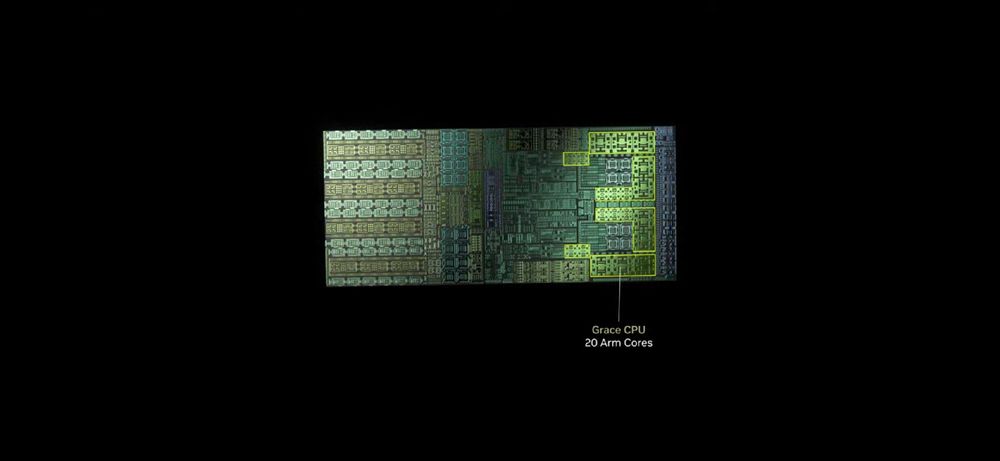

Because otherwise why would it have an asymmetric CPU layout?

Looks like 2 clusters with 5x Cortex-X + 5x Cortex-A each

It also seems to have all the I/O you'd want for a Laptop

"1000 FP4 TOPS" (24TPCs?) would correspond GB205 (5070Ti Laptop) performance

Because otherwise why would it have an asymmetric CPU layout?

Looks like 2 clusters with 5x Cortex-X + 5x Cortex-A each

It also seems to have all the I/O you'd want for a Laptop

"1000 FP4 TOPS" (24TPCs?) would correspond GB205 (5070Ti Laptop) performance

Because that was not on my bingo card

Sauce:

youtu.be/__9sJsKHBmI

Because that was not on my bingo card

Sauce:

youtu.be/__9sJsKHBmI

No way they need 6 digits + a letter to name these things

/1

No way they need 6 digits + a letter to name these things

/1

Check that the math makes sense before posting it on the internet

No Ryzen processor announced or launched has >50TOPS of "AI performance"

And RDNA3 doesn't increase performance on INT8 over RDNA2, even though it is for FP32 and "AI" FP16/BF16

Check that the math makes sense before posting it on the internet

No Ryzen processor announced or launched has >50TOPS of "AI performance"

And RDNA3 doesn't increase performance on INT8 over RDNA2, even though it is for FP32 and "AI" FP16/BF16

This includes:

-10th/11th/12th Gen Core

-13th Gen Core i9

-Core i3 N-series

-"Intel Processor"

-3rd Gen Xeon Scalable

Even if you use search, a lot of SKUs (mostly DT) seem to be gone

ark.intel.com

This includes:

-10th/11th/12th Gen Core

-13th Gen Core i9

-Core i3 N-series

-"Intel Processor"

-3rd Gen Xeon Scalable

Even if you use search, a lot of SKUs (mostly DT) seem to be gone

ark.intel.com

-Birch Stream IO Die (shared): 241mm²

-GNR 44P UCC Compute Die: 598mm²

-SRF 144E HCC Compute Die: ~578mm² (large margin of error due to low res)

-Birch Stream IO Die (shared): 241mm²

-GNR 44P UCC Compute Die: 598mm²

-SRF 144E HCC Compute Die: ~578mm² (large margin of error due to low res)

Putting all of the recent info together, BMG-G10's specs are:

-Xe² HPG architecture

-56 Xe Cores

-448 XVEs (EUs)

-2x shaders per XVE (like PVC)

-112MB Adamantine(?) Cache

-256-bit G6X bus

Putting all of the recent info together, BMG-G10's specs are:

-Xe² HPG architecture

-56 Xe Cores

-448 XVEs (EUs)

-2x shaders per XVE (like PVC)

-112MB Adamantine(?) Cache

-256-bit G6X bus

"Xilinx Alveo SN1022" is being rebranded to "AMD Alveo U45N", probably to better align with the lower end "Xilinx Alveo U25N"

SN1022 and U45N have the same specs:

xilinx.com/products/board… xilinx.com/products/board…

"Xilinx Alveo SN1022" is being rebranded to "AMD Alveo U45N", probably to better align with the lower end "Xilinx Alveo U25N"

SN1022 and U45N have the same specs:

xilinx.com/products/board… xilinx.com/products/board…

So, since Core Ultra 3 doesn't exist, what branding will 2P4E cut-down MTL-U get? Still Core Ultra 5? Regular Core 3/5? Will Intel just skip making cut-down variants of MTL-U?

So, since Core Ultra 3 doesn't exist, what branding will 2P4E cut-down MTL-U get? Still Core Ultra 5? Regular Core 3/5? Will Intel just skip making cut-down variants of MTL-U?

GH200's memory config is actually:

-96GB GPU HBM3

-480GB CPU LP5X

/1

GH200's memory config is actually:

-96GB GPU HBM3

-480GB CPU LP5X

/1

This is essentially a simplified look at "Architectural Efficiency"

This is essentially a simplified look at "Architectural Efficiency"

Big oops on my end

Big oops on my end

amd.com/en/product/121…

amd.com/en/product/121…

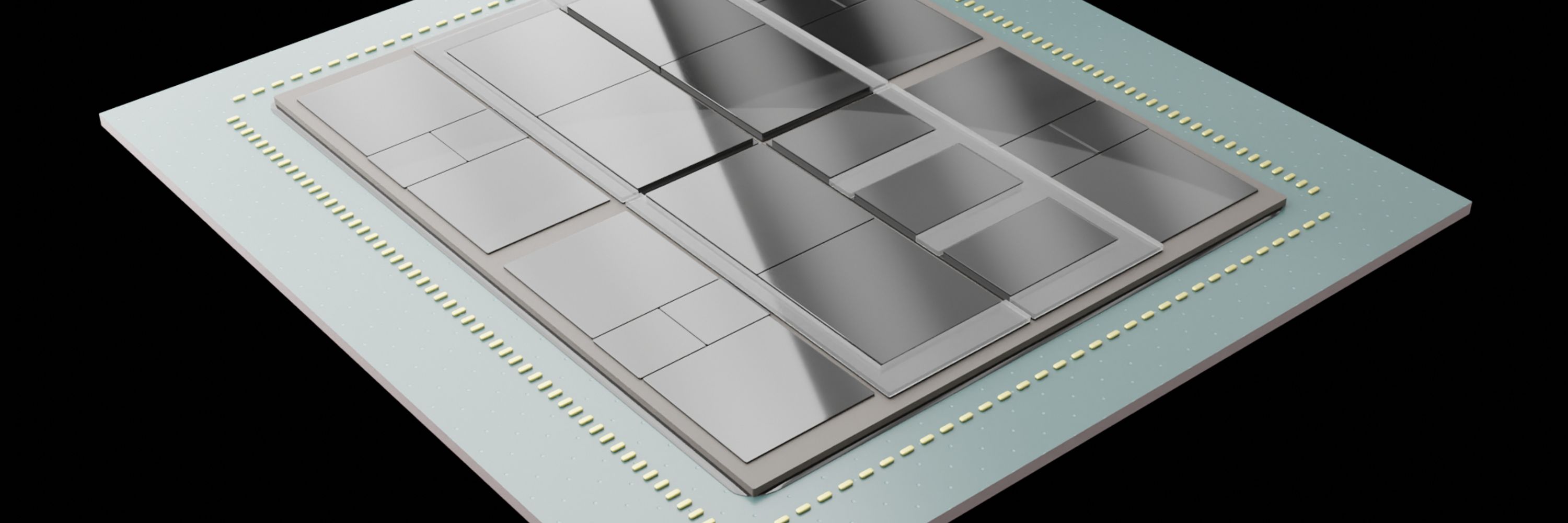

-4 Active Interposer Dies (AID)

-6 Accelerator Compute Dies (XCD)

-3 Core Complex Dies (CCD)

-8 Stacks of HBM3

-SH5 Socket

-3D Stacking

-Total of 146B Transistors

Everything is based on real dimensions, except for the top dies

-4 Active Interposer Dies (AID)

-6 Accelerator Compute Dies (XCD)

-3 Core Complex Dies (CCD)

-8 Stacks of HBM3

-SH5 Socket

-3D Stacking

-Total of 146B Transistors

Everything is based on real dimensions, except for the top dies

Intel finally released Sapphire Rapids / Golden Cove-X

Intel finally released Sapphire Rapids / Golden Cove-X

-There's an R7 7736U with lower boost than the 7735U

-There's no R9 7835HS or 7040 U-Series

-R3 7335U has a 660M iGPU with 2WGPs instead of 3

-R5 7640HS has a 760M iGPU with 4WGPs instead of 3

-7040HS clocks higher than 7045HX

-There's an R7 7736U with lower boost than the 7735U

-There's no R9 7835HS or 7040 U-Series

-R3 7335U has a 660M iGPU with 2WGPs instead of 3

-R5 7640HS has a 760M iGPU with 4WGPs instead of 3

-7040HS clocks higher than 7045HX

IDM 2.0 would seem to suggest it's an external foundry, so N3?

Mid-2023 would be pretty early for an HPC die on N3, even if it's ~100mm²

So maybe it's Intel 4?

Would be odd, but plausible for a more commercially viable successor to PVC

IDM 2.0 would seem to suggest it's an external foundry, so N3?

Mid-2023 would be pretty early for an HPC die on N3, even if it's ~100mm²

So maybe it's Intel 4?

Would be odd, but plausible for a more commercially viable successor to PVC

Wonder if it could fit on the Raphael Substrate 🤔

Wonder if it could fit on the Raphael Substrate 🤔

DGX H100 = HGX H100 (8GPU) + 2x SPR-SP

CGX = 2x(?) A16 (4GPU) + HGX Grace (2CPU)

OVX Gen2 = 4x(?) ADA? + HGX Grace (2CPU)

Maybe:

DGX GH = 4x HGX Grace Hopper ?

Would line up with what NVIDIA showed at GTC 2021

DGX H100 = HGX H100 (8GPU) + 2x SPR-SP

CGX = 2x(?) A16 (4GPU) + HGX Grace (2CPU)

OVX Gen2 = 4x(?) ADA? + HGX Grace (2CPU)

Maybe:

DGX GH = 4x HGX Grace Hopper ?

Would line up with what NVIDIA showed at GTC 2021

The larger L2 would decrease L3 Hits by ~40% following the square root rule, which would decrease pressure on the Ring bus, increasing MT Perf

/1

The larger L2 would decrease L3 Hits by ~40% following the square root rule, which would decrease pressure on the Ring bus, increasing MT Perf

/1

If so, it's definitely not on N3 (just way too big for that)

An N5-series node (or even N6) would make more sense

Wonder what they're doing with the cache system then 🤔

If so, it's definitely not on N3 (just way too big for that)

An N5-series node (or even N6) would make more sense

Wonder what they're doing with the cache system then 🤔