Software engineer at Microsoft, opinions here are my own

Still ARL idle power is just fine for a desktop platform, so maybe they didn't bother.

Still ARL idle power is just fine for a desktop platform, so maybe they didn't bother.

I also think an engineer should lead the company because they can appreciate the technical challenges/sniff out BS, and Pat Gelsinger is an engineer.

I also think an engineer should lead the company because they can appreciate the technical challenges/sniff out BS, and Pat Gelsinger is an engineer.

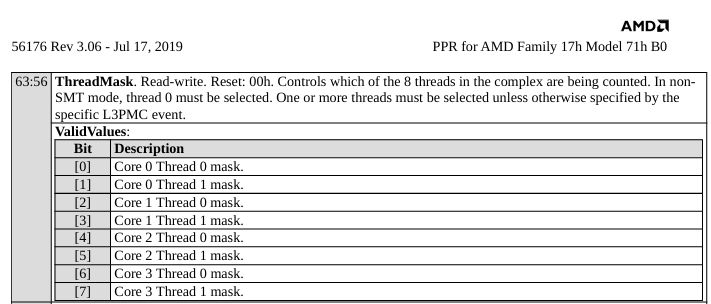

Zen 2 used eight bits, letting you select any combination of logical SMT threads within a CCX for L3 performance monitoring. More flexible, but would take too many bits with Zen 3's larger CCXes.

Zen 2 used eight bits, letting you select any combination of logical SMT threads within a CCX for L3 performance monitoring. More flexible, but would take too many bits with Zen 3's larger CCXes.