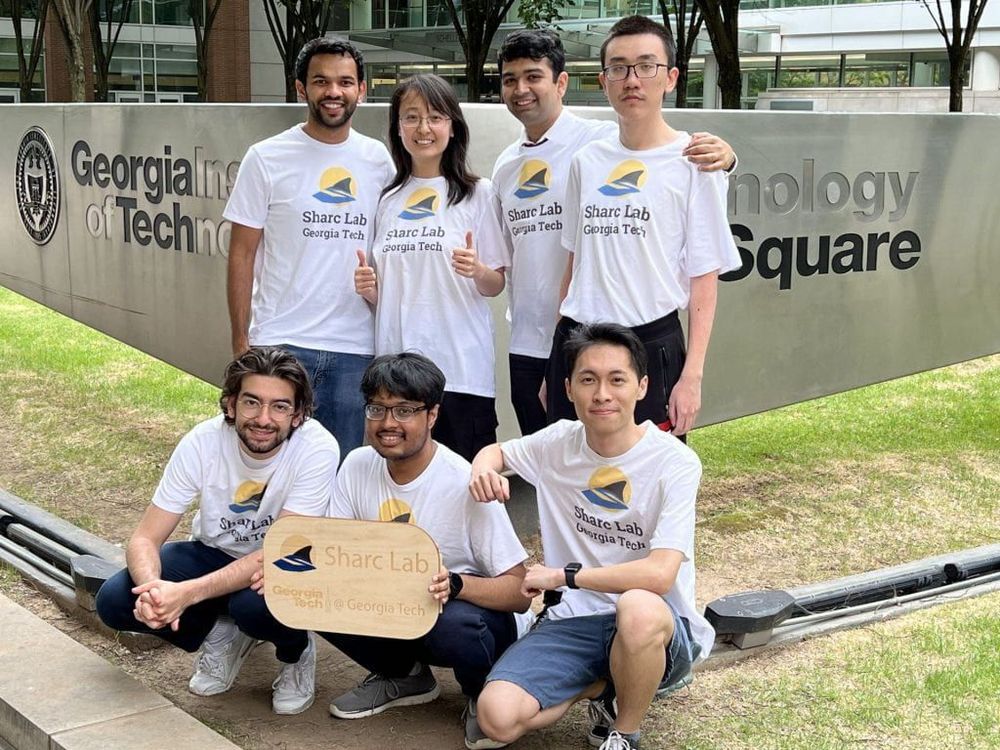

Atlanta, Georgia, USA

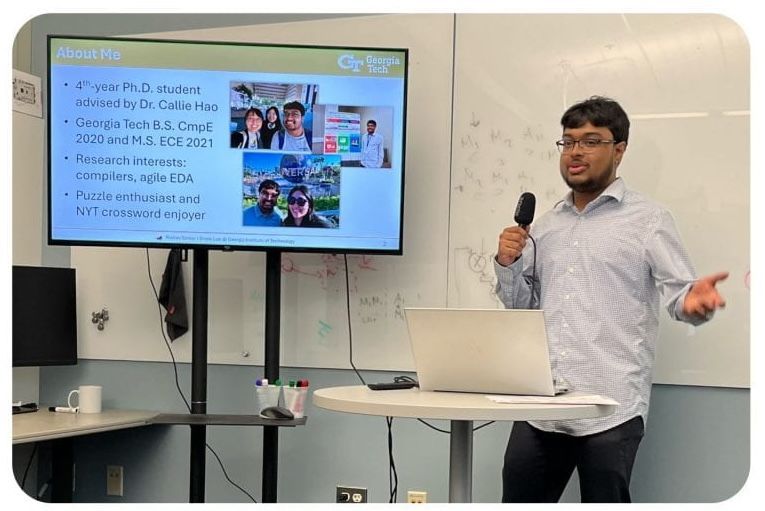

sharclab.ece.gatech.edu

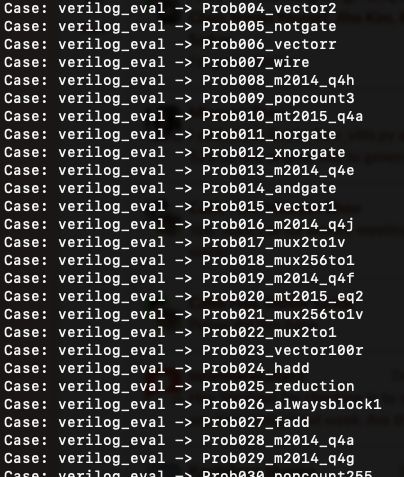

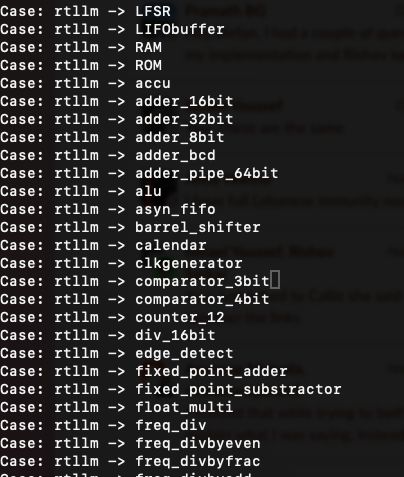

Finally working with local LLM inference after some bugs with vLLM

Finally working with local LLM inference after some bugs with vLLM

iclr.cc/virtual/2024...

iclr.cc/virtual/2024...

Slides: www.microsoft.com/en-us/resear...

Video: www.youtube.com/watch?v=z1Z5...

Slides: www.microsoft.com/en-us/resear...

Video: www.youtube.com/watch?v=z1Z5...

Still holds up as a primer on FPGAs and their use in compute accelerators.

fpga.org/2016/07/16/c...

Still holds up as a primer on FPGAs and their use in compute accelerators.

fpga.org/2016/07/16/c...

If #HPC or #supercomputing is of interest to you, please interact with this post in some way - either repost, quote, like, reply with insights or just your fav gif, tag friends, etc.

If #HPC or #supercomputing is of interest to you, please interact with this post in some way - either repost, quote, like, reply with insights or just your fav gif, tag friends, etc.

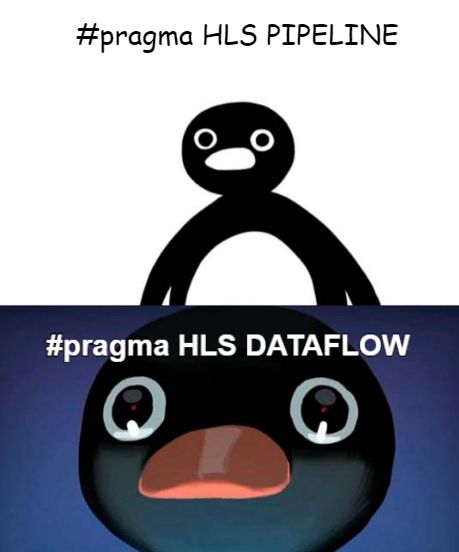

You cannot have multiple cpp files that have the same name in the same project even if they are in different directories

They might have updated this is never versions but who knows!

Discovered by my great lab mate @rishovsarkar.com

#xilinx #fpga

You cannot have multiple cpp files that have the same name in the same project even if they are in different directories

They might have updated this is never versions but who knows!

Discovered by my great lab mate @rishovsarkar.com

#xilinx #fpga

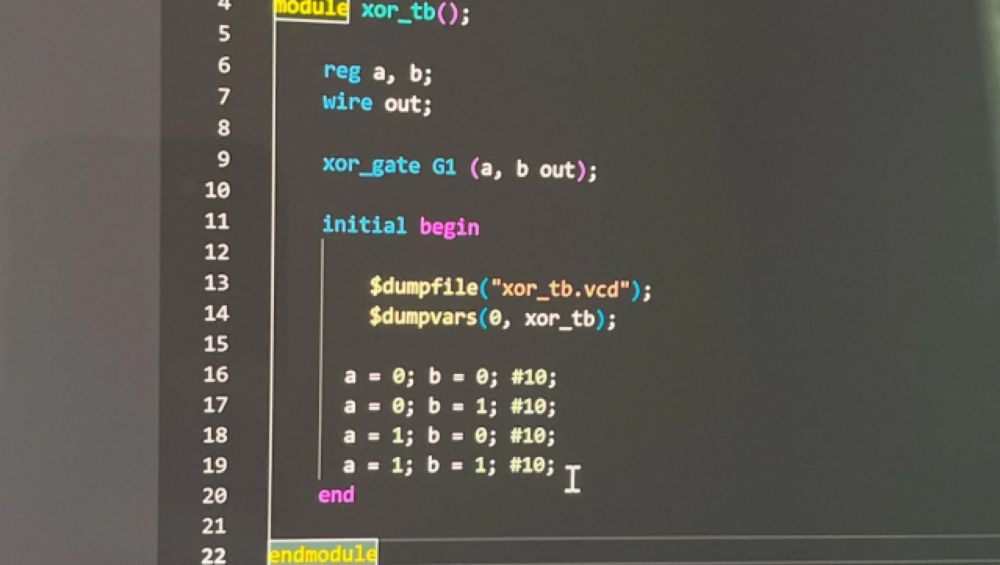

It introduces new keywords/reserved words, including “int” and “do” which appear as port names for many older designs, “int” referring to an init signal and “do” to mean “data out”.

#verilog

It introduces new keywords/reserved words, including “int” and “do” which appear as port names for many older designs, “int” referring to an init signal and “do” to mean “data out”.

#verilog

stefanabikaram.com/writing/fpga...

stefanabikaram.com/writing/fpga...

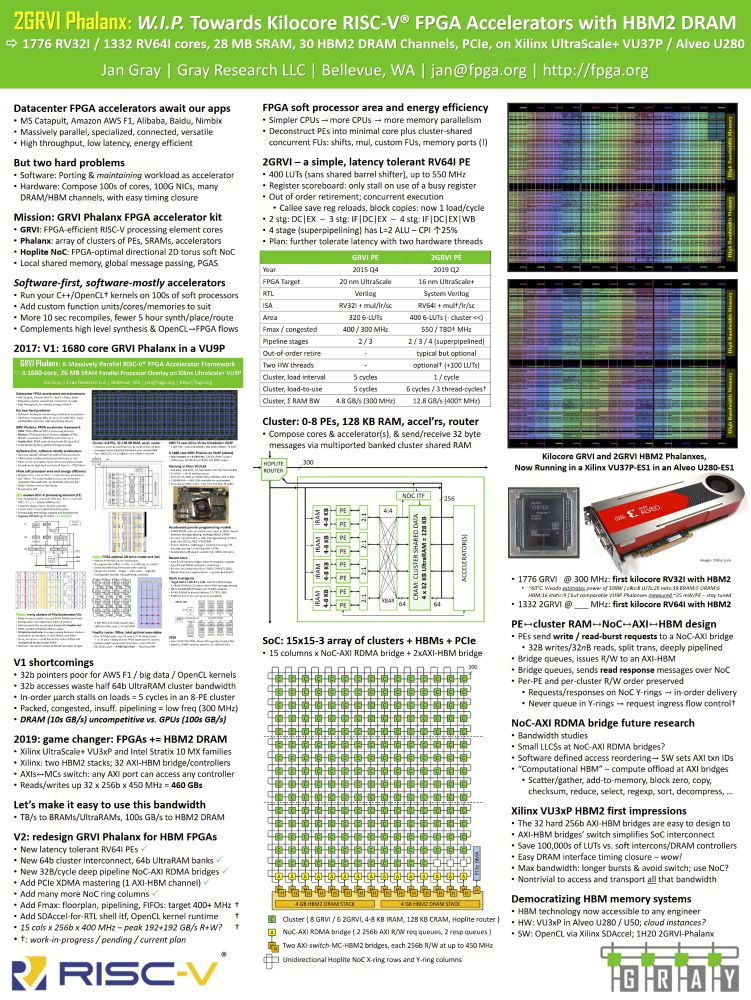

2GRVI Phalanx at Hot Chips 31: The First Kilocore RISC-V RV64I with HBM2 High Bandwidth Memory

fpga.org/2019/08/19/2...

2GRVI Phalanx at Hot Chips 31: The First Kilocore RISC-V RV64I with HBM2 High Bandwidth Memory

fpga.org/2019/08/19/2...