⚡️ FPGAs, IoT and Digital Design

🏃♂️Running and Fitness

Cat person 🐈⬛

They seem to all equally suck at this

They seem to all equally suck at this

Slower as in « more clock cycles », but these clock cycles can be much shorter, and some instruction can take less clock cycles, because the combinational path is split in shorter segments

Slower as in « more clock cycles », but these clock cycles can be much shorter, and some instruction can take less clock cycles, because the combinational path is split in shorter segments

Put it into a $readmemh to put in into « ram » (Quartus is not inferring RAM because of the combinational read, it’s using flip flops 😂)

Put it into a $readmemh to put in into « ram » (Quartus is not inferring RAM because of the combinational read, it’s using flip flops 😂)

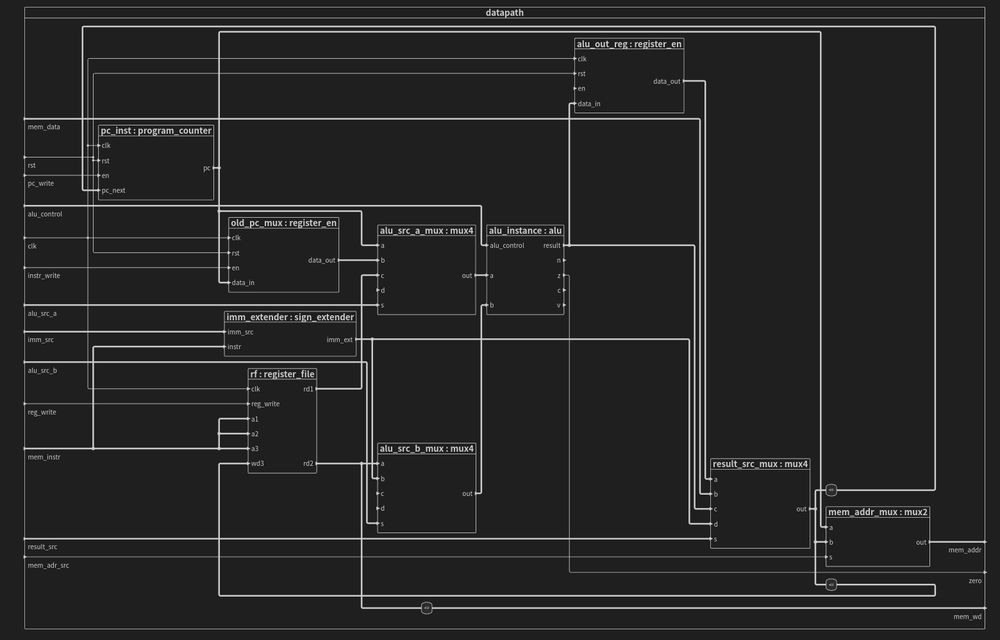

What about a custom RISC-V cpu that can run C code ?

I’ve designed a primitive single cycle RV32Ish (it’s missing a few instr) CPU and implemented it on the DE10-Lite.

It broke me 😂

What a journey it has been from the @shawnhymel.bsky.social FPGA course to this !

What about a custom RISC-V cpu that can run C code ?

I’ve designed a primitive single cycle RV32Ish (it’s missing a few instr) CPU and implemented it on the DE10-Lite.

It broke me 😂

What a journey it has been from the @shawnhymel.bsky.social FPGA course to this !

Braindead

Braindead

I'm shocked at how bad it is. Read the reviews, i was sure you were all exaggerating.

It's so bad the "Urgent notifications" thing disturbed me and urged me to respond to... a scam...

Don't get me started on the rest...

I'm shocked at how bad it is. Read the reviews, i was sure you were all exaggerating.

It's so bad the "Urgent notifications" thing disturbed me and urged me to respond to... a scam...

Don't get me started on the rest...

License plates numbers here are issued on a chronological fashion. « GV » kinda means « mid 2024 » Elon was already batshit crazy at this point.

It’s more like a « please don’t key my car »

Fuck that

License plates numbers here are issued on a chronological fashion. « GV » kinda means « mid 2024 » Elon was already batshit crazy at this point.

It’s more like a « please don’t key my car »

Fuck that

With only 1 botch wire 😂. I trusted KiCAD a bit too much with the diode footprint.

84% efficiency at 15V to 170V@20mA, not that bad, I think the transformer is not very efficient.

Micromax package was challenging to hand solder 😅

USB-C PD works!

With only 1 botch wire 😂. I trusted KiCAD a bit too much with the diode footprint.

84% efficiency at 15V to 170V@20mA, not that bad, I think the transformer is not very efficient.

Micromax package was challenging to hand solder 😅

USB-C PD works!

It’s rated for 6 IN-14 tubes @ 2mA, and works with either an USB-C PD 3.0 3A input or a direct 15VDC pin header.

I’ll open source the final revision once I’m sure it does not blow up and everything is fine

#oshw #opensource #nixie

It’s rated for 6 IN-14 tubes @ 2mA, and works with either an USB-C PD 3.0 3A input or a direct 15VDC pin header.

I’ll open source the final revision once I’m sure it does not blow up and everything is fine

#oshw #opensource #nixie

I think I need a soft charging circuit for this output cap though, listen to the coil whine at startup 😂

Vpp is less than 0.1V under a 3W load (10% of target)

Can’t wait for the next steps !! Stay tuned ⚡️

Oh and thanks @ifixit.com for the FixHub!

I think I need a soft charging circuit for this output cap though, listen to the coil whine at startup 😂

Vpp is less than 0.1V under a 3W load (10% of target)

Can’t wait for the next steps !! Stay tuned ⚡️

Oh and thanks @ifixit.com for the FixHub!

What I wanted with this one was to design a high voltage flyback converter from scratch.

I think I can downsize multiple component a fair bit but nailing the first revision (minus the diode) is already quite a miracle !

Voltage is quite high due to resistor values

What I wanted with this one was to design a high voltage flyback converter from scratch.

I think I can downsize multiple component a fair bit but nailing the first revision (minus the diode) is already quite a miracle !

Voltage is quite high due to resistor values

It combines every aspect of Digital Design and Computer Architecture, plus it’s a fun project. Here’s the power supply! (cont)

It combines every aspect of Digital Design and Computer Architecture, plus it’s a fun project. Here’s the power supply! (cont)

This seems counter intuitive but the VGA timings are tolerant enough to allow for small errors.

Even getting a clock divider cycle accurate was a challenge on itself

This seems counter intuitive but the VGA timings are tolerant enough to allow for small errors.

Even getting a clock divider cycle accurate was a challenge on itself

Writing dirty HDL code is already far from easy, but writing clean HDL is way harder !

Reading the amazing book "Digital Design and Computer Architecture" by Sarah and David Harris, I decided to implement in hardware one of the examples, the traffic light controller.

Writing dirty HDL code is already far from easy, but writing clean HDL is way harder !

Reading the amazing book "Digital Design and Computer Architecture" by Sarah and David Harris, I decided to implement in hardware one of the examples, the traffic light controller.

Your DMs are closed though 😭

Your DMs are closed though 😭

It seems that a concentricity defect between the barrel and the jack input (tested with multiple tips) is causing a really flimsy connection.

I hate to do this... but i've waited long enough, please get back to me

It seems that a concentricity defect between the barrel and the jack input (tested with multiple tips) is causing a really flimsy connection.

I hate to do this... but i've waited long enough, please get back to me