| Writer at the BitLog technology blog | #FPGA and #ASIC connoisseur | Mastodon: @ometeer@mastodon.social | Twitch: http://twitch.tv/286tech

🎸 Tuitar — A guitar training tool & DIY kit 🎛️

⚡ Runs in the terminal or standalone on ESP32.

🎵 Real-time tuning, fretboard tracking, signal analysis

🦀 Written in Rust & built with @ratatui.rs

⭐ GitHub: github.com/orhun/tuitar

#rustlang #ratatui

🎸 Tuitar — A guitar training tool & DIY kit 🎛️

⚡ Runs in the terminal or standalone on ESP32.

🎵 Real-time tuning, fretboard tracking, signal analysis

🦀 Written in Rust & built with @ratatui.rs

⭐ GitHub: github.com/orhun/tuitar

#rustlang #ratatui

The only downside is that I can't put it down once I start reading haha.

The only downside is that I can't put it down once I start reading haha.

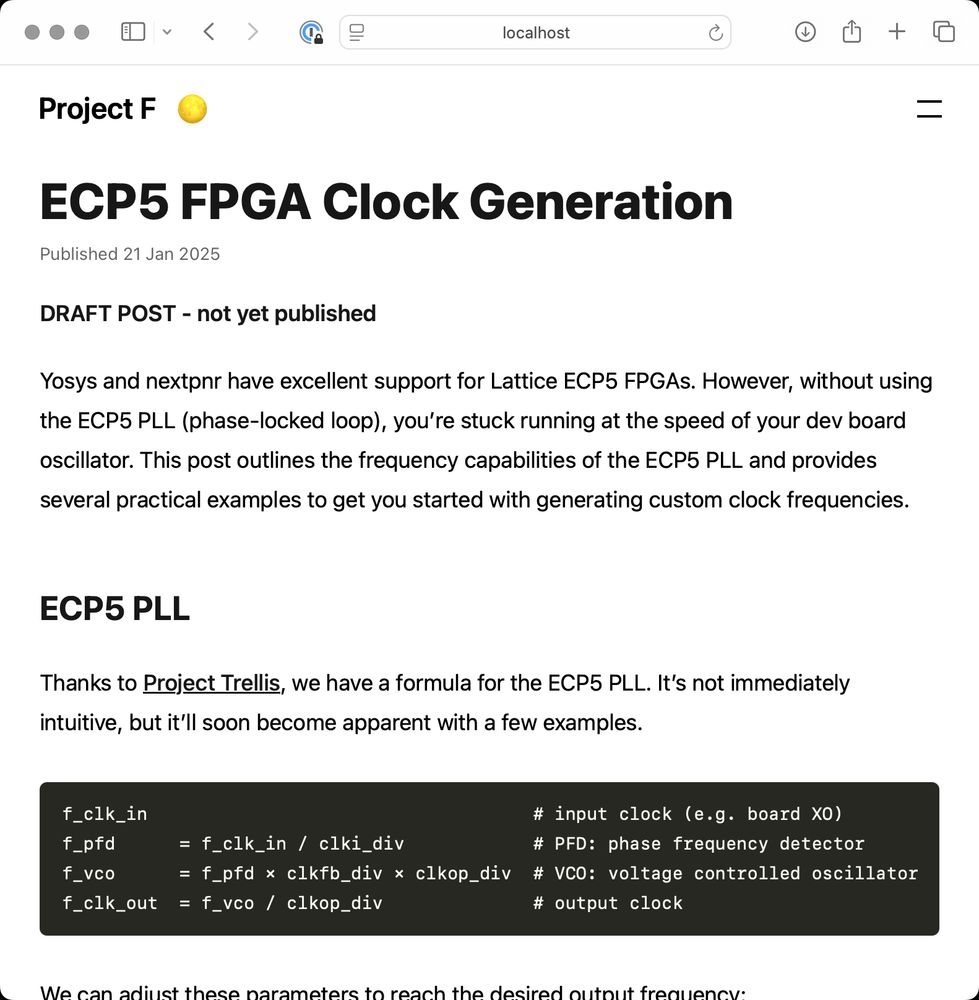

"Yosys and nextpnr have excellent support for Lattice ECP5 FPGAs. However, without using the ECP5 PLL, you're stuck running at the speed of your dev board oscillator..."

"Yosys and nextpnr have excellent support for Lattice ECP5 FPGAs. However, without using the ECP5 PLL, you're stuck running at the speed of your dev board oscillator..."

If you're interested, please let me know what days / times work for you:

doodle.com/meeting/orga...

If you're interested, please let me know what days / times work for you:

doodle.com/meeting/orga...

This interactive simulation actually lets you look inside a digital design as it’s running!

It’s a cellular automata by Alexander Mordvintsev and he taped out on Tiny Tapeout 9.

And no, it’s not a recording!

znah.net/tt09/

This interactive simulation actually lets you look inside a digital design as it’s running!

It’s a cellular automata by Alexander Mordvintsev and he taped out on Tiny Tapeout 9.

And no, it’s not a recording!

znah.net/tt09/

And other beautiful places too of course :D

And other beautiful places too of course :D

x.com/m_bitsnbites...

x.com/m_bitsnbites...

store.steampowered.com/app/1349230/...

store.steampowered.com/app/1349230/...

I'm looking for a bit of paid work (low to mid hundreds of USD) before year's end.

Most comfortable with embedded Rust and FPGA design using Amaranth HDL (and Python in general). I am willing to write C as well.

I'm looking for a bit of paid work (low to mid hundreds of USD) before year's end.

Most comfortable with embedded Rust and FPGA design using Amaranth HDL (and Python in general). I am willing to write C as well.

https://www.youtube.com/watch?v=Ge3aKEmZcqY

https://www.youtube.com/watch?v=Ge3aKEmZcqY

Went from barely 30 Mbps up/down to 920+ Mbps up/down.

Went from barely 30 Mbps up/down to 920+ Mbps up/down.