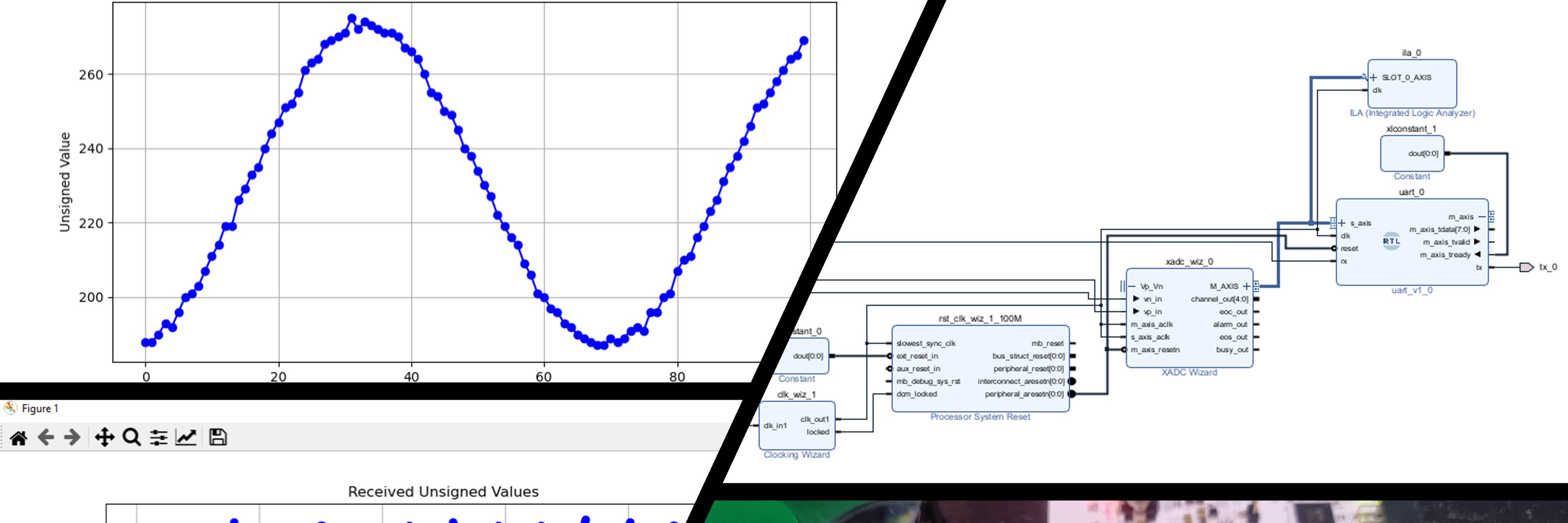

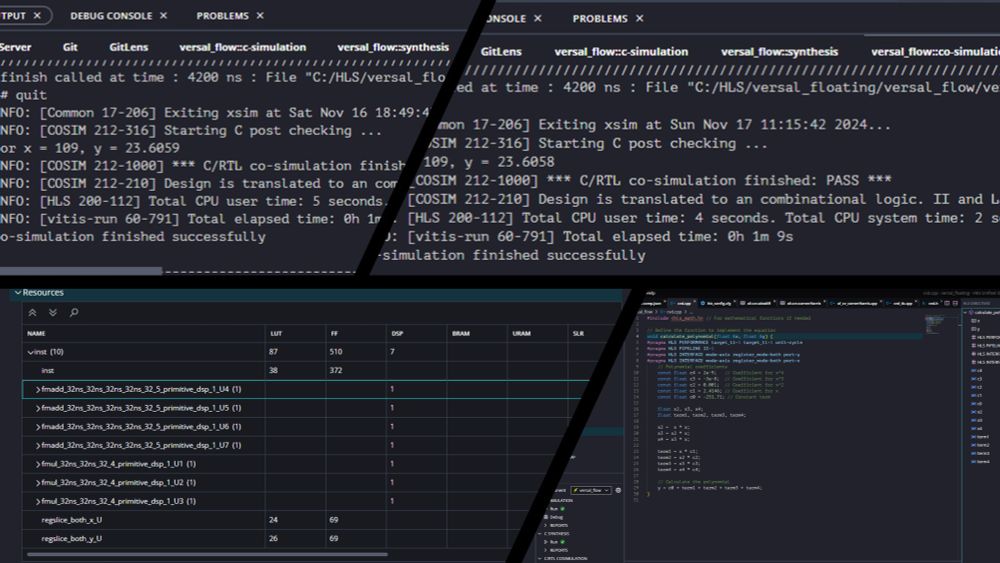

www.adiuvoengineering.com/post/microze...

www.adiuvoengineering.com/post/microze...

www.youtube.com/watch?v=5Q6K...

looking forward to what @ataylorfpga.bsky.social comes up with for next years webinars 🫡

www.youtube.com/watch?v=5Q6K...

looking forward to what @ataylorfpga.bsky.social comes up with for next years webinars 🫡

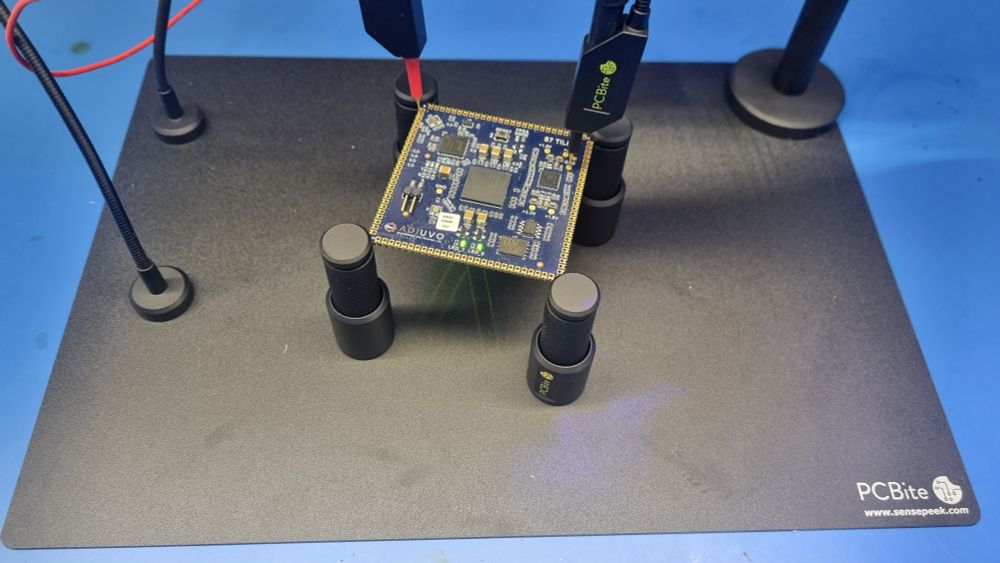

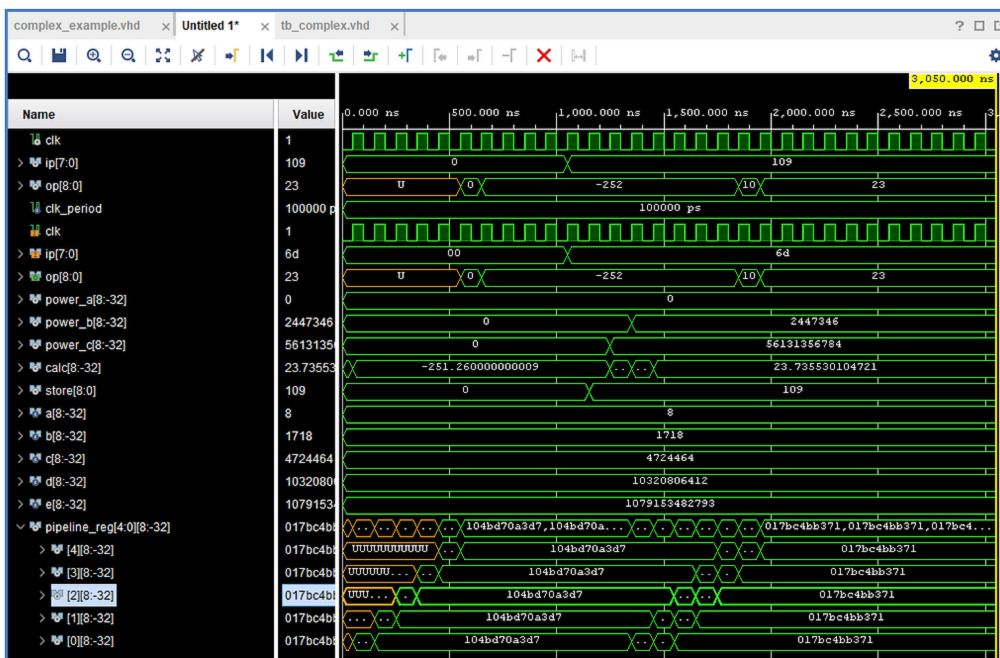

www.hackster.io/adam-taylor/...

www.hackster.io/adam-taylor/...

#fpga #engineering #embeddedsystems #electronics #embeddedsoftware

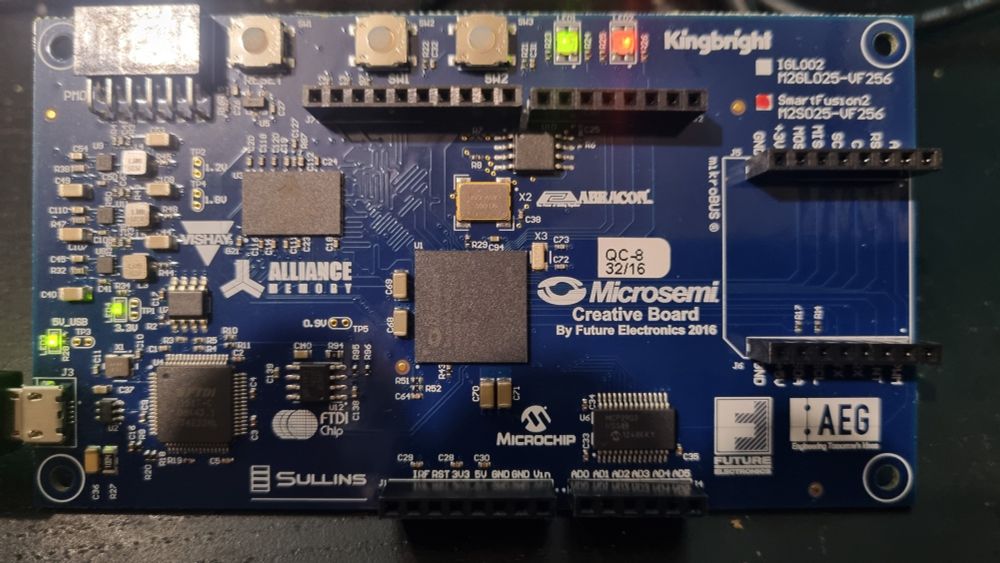

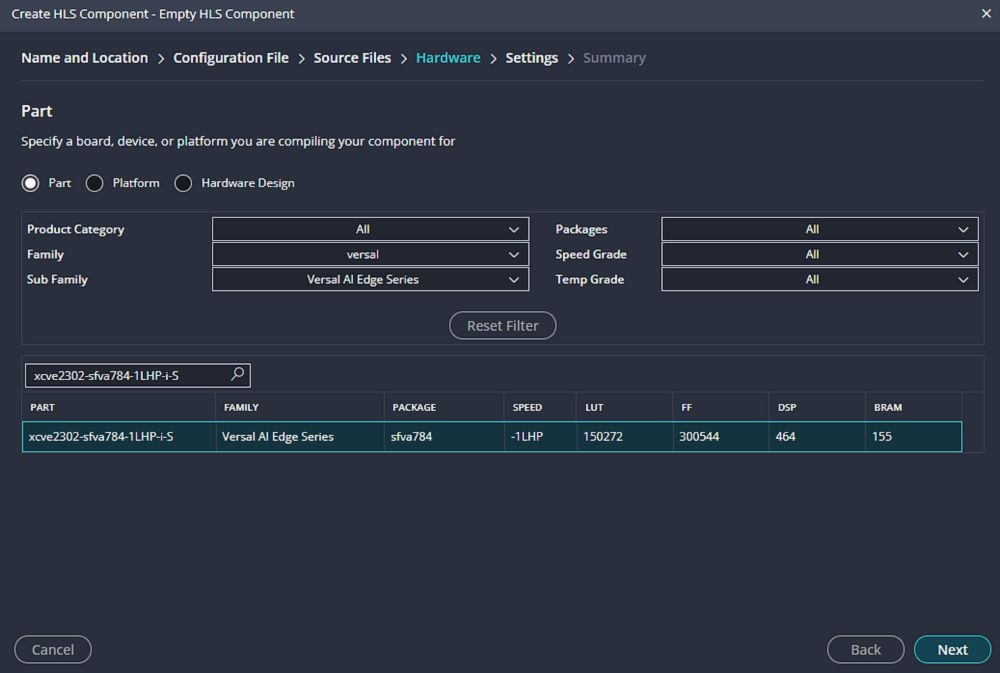

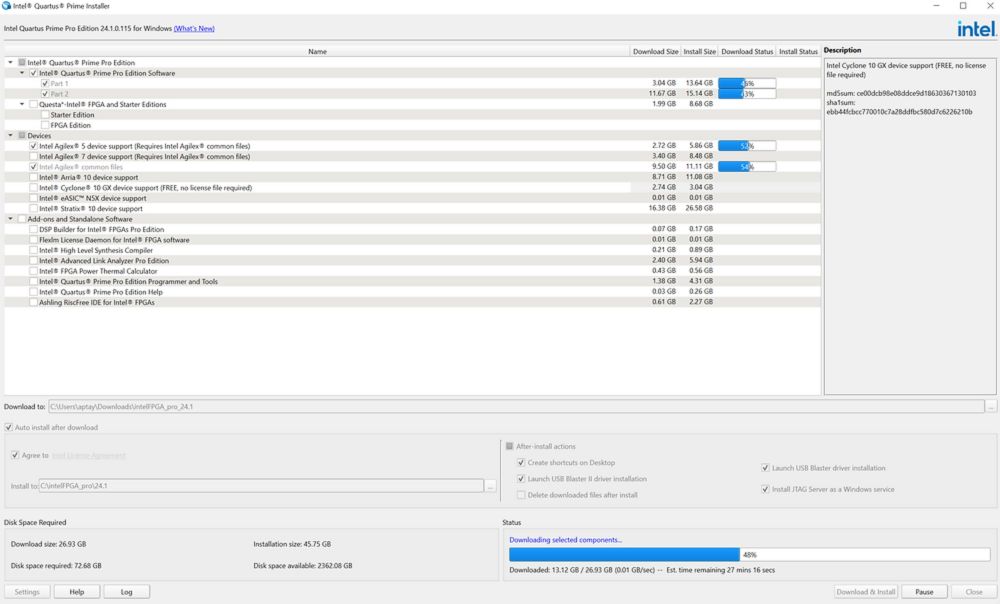

www.adiuvoengineering.com/post/altera-...

#fpga #engineering #embeddedsystems #electronics #embeddedsoftware

www.adiuvoengineering.com/post/altera-...

www.adiuvoengineering.com/post/microze...

www.adiuvoengineering.com/post/microze...

www.adiuvoengineering.com/post/altera-...

www.adiuvoengineering.com/post/altera-...

www.adiuvoengineering.com/post/microze...

www.adiuvoengineering.com/post/microze...

#fpga #embeddedsystems #engineering #embeddedsoftware #engineering

www.adiuvoengineering.com/post/microze...

#fpga #embeddedsystems #engineering #embeddedsoftware #engineering

www.adiuvoengineering.com/post/microze...